Аналоговое теле- и радиовещание активно вытесняется цифровым. Однако цифровые устройства из-за ограничений по частоте не могут полностью вытеснить аналоговые методы обработки, особенно в диапазоне СВЧ. Одним из наиболее простых и самых распространенных типов цифровой модуляции радиочастотных сигналов является, так называемая, «четырехпозиционная фазовая манипуляция» (QPSK), которая применяется в устройствах мобильной и спутниковой связи, спутниковом телевидении и т.д. В статье приведено описание разработанного в лаборатории ЧАО «РОКС» прямого QPSK-модулятора. В системах связи цифровая модуляция утвердилась уже давно. Сегодня она становится все более актуальной при передаче цифрового ТВ по каналам спутникового вещания и радиорелейным линиям. Те из читателей, которые намерены строить свою станцию спутниковой связи или радиорелейную линию для передачи сигналов цифрового ТВ (например, предназначенную для связи между двумя операторами СКТВ), должны будут решить задачу создания модулятора QPSK.

Рассматриваемый модулятор сконструирован таким образом, чтобы входящие в его состав платы можно было независимо использовать в других конструкциях. Например, плата DDS может быть частью многих систем, нуждающихся в источнике высококачественного сигнала в диапазоне до 200 МГц, имеющего очень малый шаг перестройки по частоте (менее 1 Гц). Если такой мелкий шаг перестройки не требуется, а достаточно иметь сетку частот с шагом 1 МГц, плата собственно модулятора может использоваться без платы DDS. Кроме того, в других разработках может успешно использоваться комбинированный синтезатор частот. Он может быть основой для многих радиолюбительских измерительных приборов (ГКЧ, анализаторов спектра и т.д.). Если сигнал данного синтезатора с помощью статического делителя частоты разделить по частоте на два, то получим источник сигнала в диапазоне УКВ с ок- тавной полосой перестройки, обладающий высокими спектральными характеристиками при очень малом шаге перестройки по частоте. Одним словом, данная разработка может служить подспорьем для создания многих, полезных в любительской практике устройств. В статье мы стремились также поделиться с читателями некоторыми технологическими секретами, связанными с технологией поверхностного монтажа, а также тонкостями программирования контроллера, управляющего работой комбинированного синтезатора DDS/PLL.

QPSK обычно реализуется путем сложения в аналоговом устройстве двух копий сигнала гетеродина, одна из которых является синфазной (I), а другая квадратурной (Q), т.е. сдвинутой относительно первой на 90°. Перед их сложением данные сигналы модулируются по методу двухпозиционной фазовой манипуляции (т.е. со сдвигом фазы при смене символа на 0 или 180°). Сумма двух модулированных радиочастотных компонент I и Q называется символом QPSK. Соответствующая каждому символу точка на созвездии (ансамбле сигналов) занимает одну из четырех фазовых позиций, каждая из которых представляет собой набор из двух битов. Поэтому для QPSK теоретически символьная скорость оказывается в два раза ниже битовой.

Сердцем аналоговой части модулятора является микросхема квадратурного повышающего преобразователя, в которой сигнал гетеродина разделяется на две части, и один из полученных сигналов сдвигается по фазе на 90°. В состав микросхемы входят также два смесителя, в которых I и Q компоненты гетеродина перемножаются с соответствующими сигналами основной полосы (base band). Наконец, с помощью входящего в состав микросхемы сумматора эти компоненты складываются, и в результате образуется полный модулированный сигнал. Данную микросхему некорректно называть модулятором, поскольку большая часть соответствующих стандарту DVB-S функций модуляции, предназначенных для формирования I и Q сигналов base band, реализуются в цифровой части модулятора, а квадратурный повышающий преобразователь только переносит спектр I и Q компонент base band в радиочастотный диапазон и путем их суммирования на радиочастоте окончательно формирует ансамбль сигналов. Разработанные для устройств мобильной связи микросхемы квадратурных повышающих преобразователей имеют широкий рабочий диапазон частот гетеродина, сохраняя в этом диапазоне частот достаточно высокие модуляционные характеристики (точность по амплитуде и фазе). Это позволяет строить на их основе прямые цифровые модуляторы с очень широким (больше октавы) диапазоном перестройки. Описанию одной из возможных конструкций аналоговой части прямого цифрового модулятора посвящена эта статья.

Другой важной проблемой, которую приходится решать при конструировании широкополосного прямого QPSK-модулятора, является проблема создания перестраиваемого в той же полосе частот высококачественного гетеродина. В нашей разработке применен гетеродин, выполненный по схеме синтезатора частот. Схема синтезатора частот была гибридной и представляла собой комбинацию метода синтеза сетки частот с использованием традиционной петли ФАПЧ (PLL) и метода прямого цифрового синтеза (DDS). Используется одна из разновидностей гибридной схемы, в которой сигнал, сформированный DDS, служит опорным сигналом для синтезатора PLL. Большое внимание пришлось также уделить разработке высококачественного управляемого напряжением генератора (VCO), параметры которого полностью соответствовали бы задачам данной разработки.

Конструктивно аналоговая часть модулятора QPSK состоит из 4-х связанных между собой плат, а именно:

- Платы квадратурного повышающего преобразователя и PLL-синтезатора частот (105×70 мм).

- Платы DDS и источника тактовой частоты (74×50 мм).

- Платы контроллера (64×50 мм).

- Платы стабилизаторов.

Остановимся более подробно на конструкции главных частей прямого модулятора QPSK.

Квадратурный повышающий преобразователь

Квадратурный повышающий преобразователь собран на микросхеме преобразователя частоты с фиксированным усилением типа AD8346 от Analog Devices, которая обеспечивает уровень среднеквадратичной выходной мощности -5 дБм при размахе напряжения 1,2 В на входах I и Q. Точка компрессии на 1 дБ по выходу модулятора равна 0 дБм. Уменьшение выходного уровня на 15 дБ относительно этой величины обеспечивает оптимальные параметры спектра для сигнала QPSK, равно как и уровень модулирующих входных сигналов с размахом примерно 750 мВ на дифференциальных входах I/Q, измеренный относительно смещения по постоянному току. Для схем квадратурной модуляции, в том числе QPSK, очень важно откорректировать погрешности модулятора, которые непосредственно воздействуют на величину ошибки амплитуды вектора (EVM). Радиолюбителям зачастую недоступны средства измерений, с помощью которых можно настроить параметры квадратурного преобразователя. Самый простой путь преодоления этой трудности таков: надо сделать простейшую низкочастотную схему (работающую на частотах в сотни кГц), с помощью которой полученный от низкочастотного генератора сигнал разделялся бы на два сигнала, сдвинутые точно на 90°. Полезность такой схемы будет тем большей, чем точнее будет полученный с ее помощью фазовый сдвиг. На низких частотах часто удобнее построить фазовращатели со сдвигом на +45 и -45°. Синфазный сигнал подается на смеситель I, а квадратурный — на смеситель Q. После подачи на входы квадратурного конвертора полученных таким путем сигналов на его выходе получим спектр, состоящий из несущей и двух боковых компонент, отстоящих от нее на величину частоты низкочастотного генератора, а именно LO+BB и LO-BB, где LO — частота несущей, а ВВ — частота низкочастотного генератора. Эта схема аналогична схеме смесителя с фазовым подавлением зеркальной частоты. При настройке следует добиваться как можно более сильного подавления одной из боковых частот по отношению к другой.

Рассогласование по амплитуде и фазе между I и Q сигналами, а также неточный сдвиг фазы на 90° между квадратурными составляющими сигнала гетеродина (LO) в квадратурном смесителе I/Q приводят к нежелательному появлению, например, верхней зеркальной частоты LO+BB в случае, если желаемый сигнал будет на частоте LO-BB. Если входящие в состав цифровой части модулятора ЦАП предназначены для формирования сложных выходных сигналов, то хорошее подавление зеркальных частот ЦАП на входе модулятора будет особенно важно, так как эти помехи попадают в рабочий канал.

Структурная схема радиочастотной части модулятора показана рис.1.

Неточность позиции по фазе невозможно компенсировать простыми средствами, но согласование по амплитуде может быть достигнуто относительно легко за счет независимой регулировки усиления на выходах ЦАП и точной установки напряжений смещения по входам I и Q. Предназначенные для использования совместно с описываемым здесь устройством схемы ЦАП обязательно должны выполнять функцию калибровки усиления, которая предполагает изменение выходных токов I и Q каналов на 20 дБ при высоком разрешении по току (±4%). Подавление зеркальной частоты не менее чем на 50 дБн должно гарантировать хорошее значение ошибки амплитуды вектора (EVM), так что регулирование усиления на выходах ЦАП в указанных пределах поможет с запасом обеспечить все требования стандартов. Мы в своей разработке ориентируемся на требования стандарта DVB-S. Полученный на выходе квадратурного модулятора уровень сигнала чаще всего недостаточен для обеспечения нормальной работы следующих за ним устройств (обычно это мощные повышающие преобразователи — BUC), тем более что в большинстве применений требуется регулировка этого уровня. Поэтому необходимо создать запас усиления для возможности регулировки. Для регулировки усиления мы использовали микросхему плавного управляемого напряжением аттенюатора AT-108 от МАСОМ. Усиление сигнала производится двумя микросхемами каскадируемых широкополосных усилителей SGA-0486 и GALI-6 от MiniCircuits. В превышающей октаву полосе частот эти усилители имеют заметный спад

усиления на верхних частотах. Для его компенсации перед двухкаскадным усилителем установлена пассивная компенсирующая схема, которая вносит потери на нижних частотах диапазона и не вносит на верхних. При точной настройке этой схемы можно ликвидировать зависимость выходного уровня от частоты. Он будет зависеть только от величины ослабления, вносимого переменным аттенюатором. Альтернативой этому может быть применение на выходе устройства схемы АРМ, но это увеличивает время переключения схемы на другую частоту и не всегда соответствует особенностям применения модулятора.

Краткое описание цифровой части модулятора

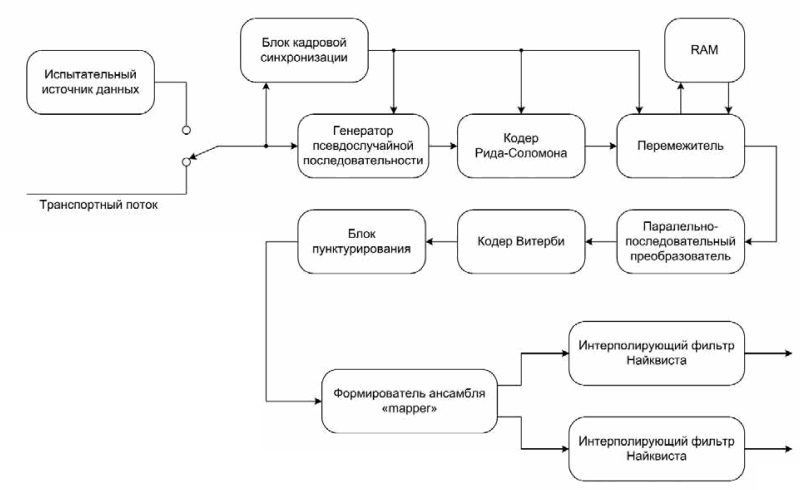

Хотя разработка цифровой части модулятора в данной статье подробно не отражена, краткое описание одного из ее вариантов поможет понять работу модулятора в целом и подходы к конструированию аналоговой части. На рис.2 показана структурная схема одного из возможных вариантов цифровой части. Он предназначен для работы с асинхронным транспортным потоком данных, передаваемых по стандартной восьмиразрядной шине параллельного интерфейса, что делает модулятор более универсальным при работе с различными кодерами и способным адаптироваться под любой из последовательных интерфейсов. Блоки, расположенные на рис.2 в двух верхних рядах, осуществляют операции над байтами, а блоки, расположенные в нижнем ряду, — над битами. Источником сигнала является либо, например, кодер MPEG-2, либо внутренний испытательный источник данных. Переключение с одного источника на другой производится с помощью джампера. Внутренний источник данных неоценим при совместной настройке цифровой и аналоговой частей модулятора. Параметры, характеризующие работу модулятора в целом, могут быть измерены с помощью специализированного анализатора спектра. Мы рекомендуем использовать для этой цели анализатор спектра типа Н-45 Compact от испанской фирмы Televes, который предназначен для проведения комплексных измерений и анализа параметров высокочастотных телевизионных аналоговых и цифровых сигналов в диапазоне частот от 5 МГц до 3,3 ГГц, в том числе в режиме изменения спектральных характеристик, регистрации импульсных и одиночных сигналов, измерения оптической аттенюации и параметров качества ВЧ сигналов, передаваемых по волоконно-оптической линии. Спектроанализаторы данного типа находят применение в качестве многофункционального профессионального инструмента для измерения параметров и анализа спектра сигналов в диапазоне частот от 5 МГц до 3,3 ГГц при монтаже и настройке антенных систем спутникового и эфирного диапазонов, при настройке аналоговых и цифровых головных станций и сетей распределения телевизионного сигнала, а также для анализа параметров оптического сигнала и модулирующих его ВЧ сигналов, передаваемых по ВОЛС. Спектроанализатор позволяет анализировать сигналы, модулированные в цифровых форматах DVB-T, DVB—C, DVB-S, DVB-S2, DVB-T2 и аналоговых форматах.

Он имеет три режима работы: измерения, телевизионный и комбо, который позволяет одновременно производить измерения параметров сигнала в режиме реального времени и просматривать на мониторе изображение выбранного канала с максимальным разрешением FULL HD 1080р. В зависимости от модификации позволяет просматривать кодированные изображения в форматах MPEG2, MPEG4, при установленном модуле САМ и сигналы с аналоговой модуляцией. Оптический вход прибора позволяет производить измерение уровня подаваемых на него оптических сигналов, а также всех параметров ВЧ сигналов, модулирующих оптику, позволяет выводить отчеты в различных файловых форматах и сохранять графики анализируемого сигнала с возможностью их последующего просмотра. С помощью этого прибора можно будет измерить основные параметры, характеризующие качество работы прямого QPSK модулятора, такие как отношение несущая/шум (C/N), коэффициенты пакетных (PER), битовых (BER) ошибок и ошибок модуляции — MER.

Рассмотрим основные узлы цифровой части модулятора с точки зрения выполняемых ими функций. Блок кадровой синхронизации извлекает сигнал кадровой синхронизации из транспортного потока с целью синхронизации остальных блоков модема. Генератор Псевдослучайной Последовательности Байтов (PRBS) скремблирует поток данных с помощью псевдослучайного сигнала, гарантируя минимальное количество переключений в сигнале, которое потребуется для синхронизации по битам в демодуляторе.

В качестве кодера прямого исправления ошибок используется кодер Рида-Соломона RS(255,239,8), укороченный до RS (204,188.8). Перемежитель (Interleaver) реорганизует поток данных. Его главное назначение состоит в перераспределении пакетных ошибок по многим кодовым словам, которые представляют собой блоки Рида-Соломона длиной по 204 байта. Он обрабатывает входящий блок, состоящий из 188 байтов (пакет транспортного потока MPEG-2), и добавляет 16 избыточных байтов, которые помогают приемнику исправлять пакетные ошибки передачи.

Блок параллельно-последовательного преобразователя преобразовывает поток байтов в поток бит, который затем поступает на сверточный кодер (кодер Витерби). Сверточный кодер производит по два бита на каждый входной бит. Для того чтобы исключить некоторые из произведенных избыточных битов, используется пунктурирование. Выбираемое с помощью джамперов кодовое отношение (отношение количества добавленных битов к общему количеству битов информации) может составлять 1/2, 2/3, 3/4, 5/6 или 7/8. За счет вариации кодового отношения изменяется как скорость передачи данных, так и степень устойчивости к ошибкам.

Затем формирователь ансамбля сигналов QPSK (mapper) из данных, поступающих на него с блока пунктурирования, производит сигнал QPSK и направляет его на два умножающих на 4 интерполирующих фильтра, реализующих характеристику типа «корень квадратный из приподнятого косинуса», которые необходимы для предотвращения межсимвольной интерференции при прохождении цифрового сигнала по радиоканалу с ограниченной полосой пропускания.

Процессор основной полосы построен на ми- KpocxeMeXilinxSpartan2XC2S200. Мы использовали плату для ПЛИС B3-SPARTAN2 + от Burch Electronic Design. Устройство используется примерно на 10% и при этом достигает тактовой частоты более 80 МГц. При этой тактовой частоте достигается символьная скорость до 20 Мсимв/с.

Поскольку указанная структура модулятора и его параметры строго соответствуют стандарту DVB-S, сформированный данным модулятором сигнал может быть принят с помощью стандартного тюнера спутникового цифрового ТВ. Это позволит создать на базе этих двух устройств радиолинию в СВЧ диапазоне. При этом скорость передачи данных, при которой достигается высококачественная передача цифрового телевидения, составляет 4,5 Мбит/с.

Аналоговая часть модулятора может работать также с низкоскоростными синхронными сигналами. Благодаря высокой стабильности частоты и низкой спектральной плотности мощности фазового шума, данный модулятор может обрабатывать самые низкоскоростные потоки плезиохронной иерархии (Т1 или Е1).

Гетеродин, требования

Поскольку в передатчике используется модуляция на нулевой промежуточной частоте (метод

прямой модуляции несущей), частота гетеродина равна центральной частоте радиоканала, самой подходящей для генерации сигнала гетеродина будет схема на основе петли ФАПЧ (PLL), которая за счет перестройки по частоте позволит сформировать нужную сетку частот с мелким шагом. Именно совокупность таких параметров, как фазовый шум на рабочей частоте, шаг перестройки частоты и время переключения частоты приводит к выбору архитектуры гетеродина в виде синтезатора частот.

Стандарт DVB-S не выдвигает очень высоких требований кточности квадратурного модулятора, но стандарт все же требует, чтобы при смешивании I и Q составляющих гетеродина с соответствующими сигналами основной полосы (base band) передатчик обеспечивал малую ошибку амплитуды вектора — EVM в своем выходном сигнале. Особенно жесткими становятся эти требования в тех случаях, когда сигналы base band являются узкополосными, т.е. символьная скорость данных является относительно низкой. Поэтому стабильность частоты гетеродина должна быть высокой, а его фазовый шум — низким. Для сигналов с модуляцией QPSK среднеквадратичное значение EVM на выходе модулятора должно быть равно 2,7%. Поэтому такие параметры, как полоса пропускания петли ФАПЧ и интегральная фазовая ошибка, являются определяющими для проекта ФАПЧ. В качестве критерия для выбора типа схемы и определения особенностей проектирования синтезатора для гетеродина в данном проекте использовалось среднеквадратичное значение полной фазовой ошибки. Типичное значение среднеквадратичной ошибки по фазе, вызванной фазовым шумом, для таких синтезаторов может быть меньше или равно 0,5°, что удовлетворительно для большинства применений. В этой конкретной системе схема ФАПЧ должна быть разработана с полосой пропускания в режиме замкнутой петли приблизительно 2,5 кГц. Задача проектирования быстрой широкополосной петли ФАПЧ в данном проекте не ставится.

Универсальный гибридный синтезатор

для УВЧ/СВЧ проектов

В основу проекта положен гетеродин с хорошей стабильностью частоты и спектральной чистотой. Синтезатор, который будет представлен здесь, обеспечивает непрерывную перестройку в полосе от 0,95 до 2,15 ГГц с разрешением при перестройке частот меньше 1 Гц и очень хорошими параметрами по фазовому шуму вблизи несущей. Он не требует никакого экзотического оборудования для своей настройки — правильно собранный он сразу будет работать. Его главное достоинство состоит в том, что он построен из доступных стандартных компонентов от Mini-Circuit, Digi-Key и Analog Devices, а его стоимость менее чем 200 дол.

Учитывая современные тенденции проектирования синтезаторов, многие из авторов при проектировании выбирают гибридную топологию PLL/DDS, в которой успешно соединяются достоинства двух технологий: метода прямого цифрового синтеза частот (DDS) и традиционной технологии синтеза на основе петли фазовой автоподстройки частоты (PLL). До того, как такой гибридный метод стал реализуемым на практике, частотный синтез по технологии PLL был сопряжен с невыгодными соотношениями между размером шага перестройки по частоте, уровнями присутствующих в выходном спектре паразитных продуктов и общей сложностью схемы синтезатора. В большинстве решений гибридных синтезаторов микросхема DDS вырабатывает стабильный, чистый и прецизионно перестраиваемый опорный сигнал для обычного синтезатора с PLL. Выходной сигнал гибридного синтезатора перестраивается с мелким шагом благодаря тому, что в качестве опорного сигнала для PLL используется сигнал DDS. Таким образом, гибридный синтезатор перекрывает диапазон частот, который типичен для синтезатора с PLL, а перестройка по частоте с мелким шагом достигается за счет использования DDS в качестве источника опорного сигнала для PLL. Доступные на сегодня DDS еще не могут работать в диапазонах УВЧ/СВЧ для того, чтобы стать полной заменой для технологии PLL. Поэтому на данном этапе технология DDS применяется для того, чтобы построить синтезатор с PLL, имеющий высокую точность перестройки по частоте, конкурентоспособную спектральную чистоту и низкую общую сложность.

Итоги: Гибридный синтезатор использует DDS как источник устойчивой, чистой и точно настраиваемой опоры для обычного синтезатора с PLL. Благодаря полученному от DDS опорному сигналу, выходной сигнал гибридного синтезатора приобретает высокую точность настройки по частоте и высокую стабильность частоты, обеспечивая диапазон перекрытия по частоте, типичный для синтезаторов с PLL.

Управление перестройкой по частоте обеспечивается через параллельный порт PC или с помощью микроконтроллера Atmel. Синтезатор может использоваться в качестве автономного стабильного источника частот УКВ/УВЧ/СВЧ, а в тех случаях, когда нужно достигнуть исключительных шумовых параметров в высокочастотных применениях с внешним дополнительным делителем частоты.

Сердце синтезатора — микросхема DDS тира AD9852 (AD9854) от Analog Devices. AD9852 используется для того, чтобы сформировать прецизионно перестраиваемый опорный сигнал для синтезатора с PLL, имеющий частоту около 10,7 МГц. При меньшей стоимости он имеет лучшие параметры, чем более популярный 10-разрядный AD9850. 12-разрядный AD9852 тактируется частотой, генерируемой либо кварцевым генератором на 10 МГц, либо внешним источником с частотой 10 МГц, при использовании встроенного умножителя тактовой частоты, который позволяет получить внутренние тактовые частоты, находящиеся в интервале от 80 до 120 МГц. После прохождения через кварцевый фильтр, служащий для подавления любых широкополосных помех, сигнал от DDS усиливается и преобразуется в прямоугольную форму с помощью компаратора LT1016 от Linear Technologies. Отфильтрованный и согласованный по уровню опорный сигнал для PLL, сформированный компаратором, вместе со сравниваемым с ним сигналом, который с помощью резистивного делителя ответвляется от VCO может быть подан на любую из микросхем программируемых синтезаторов PLL, например, относящуюся к семейству LMX2306/16/26 от National Semiconductor или семейству ADF4110/11 /12/13 от Analog Devices. Эти микросхемы PLL-синтеза- торов широко распространены, поскольку используются в устройствах радио- и сотовой связи. Их низкие цены, простота использования и доступность в небольших количествах делают их привлекательными для использования в любых любительских радиотехнических устройствах, охватывающих частоты от нижней части диапазона УКВ до частот выше диапазона 2,4 ГГц.

Генерация выходного сигнала синтезатора может быть осуществлена с помощью коммерческого генератора с варакторной перестройкой управляемого напряжением (VCO). В настоящее время такие производители, как Mini-Circuits и Synergy Microwave, предлагают разнообразные модули VCO, предназначенные для установки в обычные печатные платы, которые обладают различными диапазонами перестройки, уровнями выходной мощности, параметрами по гармоническим искажениям и шумам и имеют различные напряжения питания. В проекте синтезатора, описанном здесь, можно было бы использовать модуль VCO ROS-2150VW от Mini-Circuits, который обеспечивает внушительный диапазон перестройки 970…2150 МГц при цене приблизительно 30 дол. К сожалению, несмотря на то, что этот VCO имеет довольно высокую стоимость, он практически недоступен у нас. Поэтому в данной разработке авторы использовали обладающий примерно такими же параметрами VCO, но реализованный на дискретных компонентах.

Общие параметры петли, такие как граница устойчивости по фазе, ширина полосы и время захвата, определяются активным петлевым фильтром третьего порядка на малошумящем операционном усилителе (ОУ) ОРА27 от Texas Instruments. ОУ не только фильтрует цифровой сигнал, поступающий от чипа синтезатора PLL, но и усиливает управляющее напряжение до уровня 0,5…25 В, который необходим для реализации максимального диапазона перестройки VCO. Установленная за VCO микросхема усилителя MGA81563 от Agilent обеспечивает усиление приблизительно на 16 дБ. От VCO через резистивный делитель сигнал поступает на выходной разъем с уровнем в середине полосы приблизительно +10 дБм и с меньшим, чем на ±2 дБ изменением уровня при перестройке частоты в пределах от 1000 до 1800 МГц.

Параметры синтезатора частот

Решающий параметр для любого синтезатора частот с PLL — это спектральная чистота его выходного сигнала. Фазовый шум, известный, как «джиттер», вызван случайными кратковременными экскурсами фазы несущей, и может быть следствием множества причин. Амплитудный шум — другой аспект комплексных шумовых параметров, наблюдаемых с помощью измерительного приемника или анализатора спектра, но он является обычно менее значащим по сравнению с джиттером фазы/частоты. Несущественным в нашем применении амплитудный шум является потому, что сигнал гетеродина, в конечном счете, подается на входы смесителей, которые по отношению к сигналу гетеродина ведут себя как ограничители, ликвидирующие флуктуации амплитуды. Наконец, в дополнение к композитному АМ/РМ шуму, выходной сигнал синтезатора может также содержать дискретные паразитные продукты, которые проявляются как боковые спектральные составляющие или с одной, или с обеих сторон от несущей.

По сравнению с простым каскадом LC-генератора, для VCO, работающего в составе петли PLL, факторы, которые могут способствовать возникновению шумов и помех в выходном сигнале, являются слишком многочисленными, чтобы можно было учесть их все. Самое плохое — это то, что невозможно охарактеризовать конкретный синтезатор одним единственным параметром «спектральной чистоты», который позволил бы прямо сравнить его с конкурентами. Влияние шумов и помех носит двойственный характер, поэтому оценить их вклад в общие параметры синтезатора довольно сложно. Мы должны принять во внимание и их амплитуду относительно сигнала несущей и величину отстройки от частоты несущей, для которой был измерен рассматриваемый эффект. J1 юбой синтезатор должен быть тщательно разработан с целью минимизации шумов и помех при таких отстройках от несущей, при которых эти шумы и помехи потенциально могут ухудшить параметры передатчика или приемника, в котором данный синтезатор используется.

Детальное обсуждение причин появления шумов и средств борьбы с ними выходит за рамки данной статьи. Короче говоря, наш анализ шумов PLL и паразитных продуктов в спектре сигнала будет ограничен учетом шумов опорного генератора, шумов VCO и эффекта умножения в петле. Очень важен правильный расчет петлевого фильтра, поскольку ширина полосы петли должна соответствовать параметрам VCO. Также важно учесть воздействие внешних по отношению к петле источников шумов и помех, таких как шумы источника электропитания и эффекты интермодуляции, наблюдаемой между различными частями схемы.

Эффект умножения в петле и связанные с опорным сигналом шумы и помехи

Любая замкнутая петля фазовой автоподстройки частоты в пределах своей полосы усиливает амплитуду фазового шума источника опорной частоты на 20 lg (N) дБ, где N — общий коэффициент умножения частоты петлей. Любые дискретные паразитные продукты в спектре опорного сигнала, находящиеся в пределах ширины полосы петли, будут также усилены на эту величину. Отметим, что при этом отстройка частоты этих паразитных продуктов от выходной несущей останется той же самой, что и их отстройка от частоты опорного сигнала.

Рассмотрим синтезатор с выходной частотой 1 ГГц и шириной полосы петли 3 кГц, опорная частота которого составляет 1 МГц, и который имеет дискретные боковые полосы с частотами в ±1 кГц и с уровнем -80 дБн. В этом случае N = 1000, а 20 Lg (N) равно 60 дБ. В выходном спектре синтезатор продемонстрирует боковые полосы с отстройкой ±1 кГц и с уровнем -20 дБн, которые, скорее всего, не будут приемлемыми для многих практических применений. Поэтому для работающей в микроволновом диапазоне PLL, которая имеет высокий коэффициент N, важно использовать высококачественный источник опорного сигнала или, если это затруднительно, то при наличии высококачественного VCO нужно использовать петлю с очень узкой полосой. Параметры по фазовому шуму у DDS очень высокие. Они определяются или шумом его собственного опорного генератора (как правило, это высококачественный кварцевый генератор), или ограничениями по уровню шумового окна, характерными для конкретного технологического процесса изготовления микросхемы DDS (как правило-140 дБн/Гц для технологии ECL и -150 дБн/Гц или лучше для современных CMOS микросхем, таких, как AD9852). Однако, в то время как его параметры по фазовому шуму удовлетворяют большинству применений, в выходном сигнале DDS в боковой полосе неизбежно присутствуют дискретные паразитные компоненты из-за дискретности фазы и погрешности выбора времени в справочной таблице для ЦАП. Они часто достаточно заметны для того, чтобы сделать невозможным использование автономного DDS в качестве первого гетеродина в высококачественном коротковолновом приемнике. Дискретные паразитные составляющие спектра в опорном сигнале DDS могут появиться в выходном сигнале синтезатора при значительных отстройках от несущей, медленно спадая за пределами ширины полосы петли, и будут усилены на 20lg (N) дБ в пределах полосы петли (см. пояснения выше).

В действительности уязвимость нашей петли для паразитных компонентов, присутствующих в опорном сигнале, больше, чем можно было бы ожидать. Чипы PLL и от National Semiconductor (LMX2326), и от Analog Devices (ADF4112) демонстрируют явную тенденцию реагирования на помехи в опорном сигнале в интервалах отстроек, соответствующих их внутренней частоте сравнения от DC до 100 МГц и вне нее.

Рассмотрим петлю с частотой сравнения 1 МГц, которая получается путем программирования модуля делителя опорного сигнала (R) в чипе PLL, равного 10-ти, при частоте произведенного DDS сигнала 10 МГц. Как и ожидалось, паразитные компоненты DDS, располагающиеся близко к опорному сигналу 10 МГц, появляются в выходном сигнале синтезатора, как было отмечено выше. Кроме того, любые паразитные компоненты DDS, появляющиеся около интервалов в 1 МГц по обе стороны от опорной частоты 10 МГц, появятся в выходном сигнале точно так, как будто они были произведены около 10 МГц. Например, помеха с частотой 7,001 МГц вызовет появление в выходном сигнале синтезатора паразитных спектральных компонентов с отстройкой ±1 кГц от несущей. Этот эффект был отмечен на оценочной плате для микросхемы National также, как и на нашем опытном образце синтезатора на основе микросхемы ADF4112. Ясно, что только фильтра нижних частот, фильтрующего опорный сигнал DDS, будет недостаточно — мы должны использовать полосно-про- пускающий фильтр для того, чтобы подавить по возможности все помехи, распределенные по всему RF спектру.

В нашем синтезаторе задача подавления помех от DDS решается с помощью строго ограничивающего полосу опорного сигнала для петли PLL недорогого монолитного 4-резонаторного кварцевого фильтра. При использовании такого фильтра с шириной полосы 15 кГц, ряд автоматизированных измерений, проведенных на случайно выбранных частотах, располагающихся в интервале между 1000 и 1800 МГц, не выявил заметных паразитных компонентов на какой-либо из частот. Без фильтра общие параметры спектра синтезатора были намного хуже. В этом случае почти для каждой случайно выбранной частоты была отмечена, по крайней мере, одна значимая паразитная компонента.