Цифровые CTB ресиверы GOLDEN INTERSTAR GI—S770CR и GI—S805CI семейства Xpeed Class широко известной западногерманской фирмы GOLDEN INTERSTAR прочно завоевали в конце первого десятилетия нынешнего время рынок восточной Европы. Особой популярностью ресиверы пользуются в европейской части России, на Украине, Белоруссии и странах Прибалтики. Этому способствовало заявленное европейское качество аппаратов.

Ресиверы были спроектированы по заказу фирмы GOLDEN INTERSTAR в Корее и выпускались в Китае.

На практике заявленные высокие эксплуатационные характеристики фактически не обеспечивались. Этому способствовало как применение некачественных пассивных электронных компонентов, так и технологические просчёты при сборке конечных устройств. Всё это свело на нет применение новейших ИМС (в частности, мощного однокристального декодера фирмы RENESAS), имеющих высокие эксплуатационные характеристики.

Достаточно хорошее результирующее качество принимаемого изображения ТВ программ, а также относительно приемлемая цена конечного устройства привели к насыщению рынка электронной техники, стран СНГ данными моделями. В эксплуатации находится большое количество аппаратов, требующих ремонта. Ниже приводятся принципиальные схемы ресиверов GOLDEN INTERSTAR GI-S770CR и GI-S805CI Xpeed Class. А также принципы их функционирования. Кроме того, в статье дана информация об однокристальном декодере uPD61217, на котором собраны описываемые ресиверы. Интересной особенностью ресивера является наличие USB порта для подключения внешней FLASH USB памяти.

Основные характеристики

CTB ресиверы GOLDEN INTERSTAR GI-S770CR Xpeed Class (далее GI-S770CR) и GOLDEN INTERSTAR GI-S805CI Xpeed Class (далее GL-S805CI) собраны на ИМС однокристального декодера для цифровых абонентских терминалов uPD61217 (описание будет приведено далее в статье) фирмы RENESAS ELECTRONICS, входящую в японскую корпорацию NEC. Данная ИМС имеет на своём кристалле стандартный набор для декодирования транспортного мультиплексированного потока TS многопрограммного ТВ и радиовещания. Основные характеристики ресиверов GI-S770CR (рис.1) и GI-S805CI следующие: система приёма DVB-S (MPEQ-2) с возможностью запоминания настройки на 6000 каналов спутникового телевидения и радиовещания. Имеется русифицированное навигационное меню EPQ, возможность вывода на экран данных телетекста. Для управления внешними устройствами (конвертерами, позиционером и т.д.) используется поддержка протоколов DiSEqC 1.0 – DiSEqC 1.2 и USALS. Ресиверы снабжёны USB портом, что позволяет получить дополнительные эксплуатационные функции. Это одновременный просмотр программ в пределах одного пакета TS, многократный просмотр фрагмента трансляции, воспроизведение с USB FLASH MP3 аудио программ и изображений в стандарте JPEG. Программное обеспечение (ПО) ресиверов можно обновлять з помощью компьютера через последовательный интерфейс RS-232 (скорость передачи 115,2 Кбит/с) или с FLASH USB. У ресиверов имеются выходы RCA CVBS, RCA YPbPr SCART (у последнего имеется функция вывода сигналов RGB, YPbPr в студийном качестве). Габаритные размеры GI-S770CR ─ 340×205×60 мм, а GI-S805CI ─ 260×215×44 мм.

Основные характеристики ресиверов GI-S770CR (рис.1) и GI-S805CI следующие: система приёма DVB-S (MPEQ-2) с возможностью запоминания настройки на 6000 каналов спутникового телевидения и радиовещания. Имеется русифицированное навигационное меню EPQ, возможность вывода на экран данных телетекста. Для управления внешними устройствами (конвертерами, позиционером и т.д.) используется поддержка протоколов DiSEqC 1.0 – DiSEqC 1.2 и USALS. Ресиверы снабжёны USB портом, что позволяет получить дополнительные эксплуатационные функции. Это одновременный просмотр программ в пределах одного пакета TS, многократный просмотр фрагмента трансляции, воспроизведение с USB FLASH MP3 аудио программ и изображений в стандарте JPEG. Программное обеспечение (ПО) ресиверов можно обновлять з помощью компьютера через последовательный интерфейс RS-232 (скорость передачи 115,2 Кбит/с) или с FLASH USB. У ресиверов имеются выходы RCA CVBS, RCA YPbPr SCART (у последнего имеется функция вывода сигналов RGB, YPbPr в студийном качестве). Габаритные размеры GI-S770CR ─ 340×205×60 мм, а GI-S805CI ─ 260×215×44 мм.

Ресивер GI-S770CR имеет DVB-CSA дескремблер и предназначен для просмотра кодированных каналов по системе скремблирования CRYPTOWORKS, оснащён интерфейсом картридера ISO-7816. Cуществует ПО ресиверов, обеспечивающее просмотр программ скремблированных в других системах условного доступа (например, VIACCESS). Для реализации данной возможности необходимо установить, используя нижеприведённый метод обновления, требуемое ПО.

Встроенный DVB-CSA дескремблер в ресивере GI-S805CI не используется. Для просмотра кодированных каналов ресивер оснащён двумя CI интерфейсами, в которые можно устанавливать САМ модули для декодирования скремблированных программ. Это позволяет использовать ресивер для приёма платных программ, кодированных по различным системам криптографии.

Эксплуатационные характеристики и функциональная схема

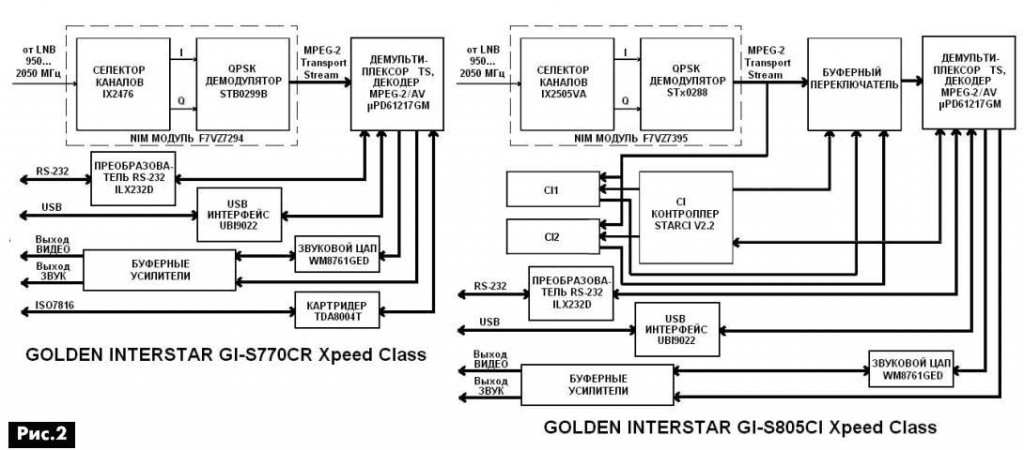

Структурная схема ресиверов GI-S770CR и GI-S805CI показана на рис.2. Входной DVB-S сигнал от понижающего конвертора в диапазоне 950…2150 МГц подаётся на вход Full-NIM модуля F7VZ7294 (GI-S770CR) и F7VZ7395 (GI-S805CI) фирмы SHARP. Приём программ возможен в режимах МСРС (множество программ на одной несущей) и SCPC (одна программа на одной несущей). Входной РЧ преобразователь на ИМС IX2476 (F7VZ7294) и IX2505VA (F7VZ7395) производит настройку ресивера на несущую требуемого канала, а также осуществляет преобразование входного сигнала на нулевую промежуточную частоту и выделяет из него I и Q составляющие.

Для изменения поляризация принимаемого сигнала используется стандартный метод, использующий инжекцию в кабель снижения постоянного напряжения питания конвертора 13,5 или 18 В. Поддиапазоны Ku-диапазона выбираются путём подачи в кабель снижения синусоидального немодулированного сигнала частотой 22кГц и амплитудой 0,6 В. Управления напряжением питания и подачей тонального сигнала осуществляет схема, выполненная на дискретных элементах. Помимо этого, управляющая схема инжектирует в кабель снижения команды, сформированных на основе протоколов, DiSEqC 1.0 – 1.2 и USALS (DiSEqC 1.3) для управления внешними дополнительными устройствами (поворотными механизмами, переключателями конверторов).

С РЧ преобразователя сигналы I и Q составляющих поступают на QPSK демодулятор, выполненный на ИМС STB0299B (F7VZ7294) и STx0288 (F7VZ7395) фирмы ST Microelectronics, которая осуществляет их стандартную демодуляцию. Демодулятор обрабатывает QPSK сигналы со скоростями потока 1…45Мбит/с. Коррекция ошибок декодера свёрточного кода Виттерби может принимать значения: 1/2, 2/3, 3/4, 5/6, 7/8 (при длине кодового органичения К=7). Декодирование внешнего кода, корректирующего ошибки, производится декодером Рида-Соломона.

В отличие от широко распространенной ИМС QPSK демодулятора STV0299В, применявшейся в DVD-S ресиверах ранее, STx0288 имеет улучшенные эксплуатационные характеристики. Положительным моментом является то, что в STx0288 добавлена функция «слепого» сканирования. Данная функция позволяет ресиверу за короткий промежуток времени просканировать весь выделенный для диапазон, не зная параметров передачи транспондеров (частоты приёма, скоростей потока, кодовых значений).

В ресивере GI-S770CR полученный сигнал поступает непосредственно на вход ИМС uPD61217. В ресивере GI-S805CI транспортный поток TS Full-NIM модуля поступает на коммутатор СІ интерфейсов, управляемый специализированным контроллером СІ интерфейса STARCI V2.2(фирмы I&C TECHNOLOGY CO.,LTD.). TS проходит либо через САМ модуль, либо поступает непосредственно на ИМС декодера.

СІ интерфейс использует для своей работы технологию клиент ─ сервер. САМ модуль использую клиентское приложение, получает доступ к ресурсам, предоставляемых сервером (хост-процессором ресивера). СІ процесс, выполняемый ресивером, обеспечивает предоставление ресурсов(хостинг).

Специализированный контроллер СІ интерфейса позволяет СІ процессу осуществлять адресный

доступ к двум независимым САМ модулям условного доступа и на аппаратном уровне управляет обменом между модулем и ресивером.

Полученный с СІ контроллера (в GI-S770CR c Full-NIM модуля) сигнал TS поступает на вход ИМС uPD61217и обрабатывается DES-дескремблером.

Если Если ресивером принимается FTA программа, роутер потока TS передаёт сигнал непосредственно на TS демультиплексор, минуя DES-дескремблер. Мощное процессорное ядро декодирует сигнал TS в сигналы изображения и звукового сопровождения, требуемого ТВ канала, а также осуществляет сервисные функции управления и контроля работы ресивера. С выхода роутера сигнал TS демультиплексируется. При этом из него выделяется требуемый ТВ или РВ канал, либо сигналы данных сервисной информации. Программа декодируется в MPEG-декодере (MPEG-2 MP@ML ISO/IEC 13818), при этом обработкой звукового сопровождения занимается субпроцессор в составе ИМС uPD61217.

Декомпрессированный видеосигнал в форматах 4:3 или 16:9 (720 пикселей на 576 строк при частоте полей 50 Гц) с выхода декодера преобразуется DENС кодером в аналоговую форму. Цифроаналоговое преобразование стерео- или моно звукового сопровождения осуществляется ИМС WM8761GED фирмы WOLFSON. Аналоговые сигналы поступают на буферные выходные усилители видео- и звукового сигналов, выполненные на широкополосном ОУ FMS6146 фирмы FAIRCHILD и дискретных элементах.

Выходные сигналы ресивера можно получить как в композитном (видеосигнал ПЦТВ на выходах RCA-CINCH и SCART), так и компонентном (YPbPr, RGB SKART и YPrPb RCA-CINCH) видах. Использование компонентного выхода позволяет получить на экране ТВ приёмника Изображение студийного качества. Сигналы звукового сопровождения так же, как сигналы изображения выводятся как на RCA, так и на SCART разъёмы.

Ресивер кроме ТВ и РВ программ позволяет принимать сервисную информацию: телетекст, субтыри. Память ресивера сохраняет настройки 6000 принимаемых каналов. При наличии в USB слоте FLASH памяти возможна запись на неё фрагментов транслируемых программ, воспроизведение записанных на неё МРЗ файлов, просмотр статических JPEG изображений. Управление, настройка системы и параметров приёма осуществляется с помощью меню с удобной экранной графикой OSD.

Установленный в ресивере GI-S770CR картридер осуществляет обмен данных с сматр-картами системы условного доступа CRYPTOWORKSи соответствует стандарту ISO 7816. При изменении (модефикации) ПО, использующего программный дескремблер других систем условного доступа, возможна устойчивая работа ресивера со смарт картами различных провайдеров, использующих иные системы криптографии программ.

Основные характеристики ИМС однокристального декодера для цифровых абонентских терминалов uPD61217

ИМС uPD61217 входит в семейство AMMASL, включающее в себя ещё ИМС uPD61210 – uPD61216. Все ИМС описываемого семейства (за исключением uPD61216) имеют двухпроцессорную архитектуру, основное ядро которого основано на MIPS ®4KEc архитектуре. Помимо основного ядра, обеспечивающего пользовательский интерфейс, функционирование в реальном времени операционной системы, на кристалле содержится субпроцессорное ядро с архитектурой 4 KEm для процессов декодирования входного сигнала, основная функция которого – поддержка декодирования звукового сопровождения (в uPD61216 субпроцессор отсутствует). Оба ядра функционируют на частосте 186 МГц с быстродействием 284 MIPS и имеют по два 4 Кбайт кеша команд и данных (Instruction — cache и Data — cache).

Унифицированный интерфейс памяти UMI (Unifed Memory Interface) поддерживает внешнюю синхронную SDRAM память со объёмом до 64 Мбайт (uPD61217 работает с DDR памятью объёмом до 168 Мбайт), которая может использоваться всеми узлами декодера. Для доступа к более медленным устройствам используются ROM/GIO интерфейсы. Интерфейс ROM позволяет подключать внешнюю NOR/NARD FLASH память объёмом до 64 Мбайт. К интерфейсам в хост-режиме также можно подключать PCMCI слоты для САМ модулей.

ИМС семейства предназначены для работы в приёмных системах как спутникового, так и наземного вещания ТВ программ стандартной разрешающей способности Standart Defenition. Входные данные транспортного потока TS вводятся в ИМС в паралельном или последовательном виде со скоростью до 100Мбит/с и обрабатываются демультиплексором. Встроенный DES-дескремблер позволяет производить декодирование с 16 парами секретных ключей. Декомпрессия осуществляется по стандарту MPEG-2 MP@ML. Все ИМС, кроме uPD61216 поддерживают возможность декодирования звука в формате DOLBY®DIGITAL (помимо стандартной декодировки двух звуковых слоёв Layers 1, 2 MPEG-2).

На выходе декомпрессора имеется графический процессор, улучшающий качество изображения, обеспечивающий наложение экранной графики на изображение. Сигнал изображения обрабатывается четырьмя цифроаналоговыми преобразователями ЦАП и передается на выход в стандартном виде, включая врезку дополнительной информации (телетекст, субтыри). Все ИМС, кроме uPD61210, могут формировать в выходном сигнале вставки системы защиты от копирования MACROVISION™7.1.

ИМС имеют возможность активации процедуры защиты от копирования АСР программ (Anti Copy Process), разработанной фирмой ROVI Corporation. Технология доступна только авторизованным клиентам фирмы ROVI.

На кристалле ИМС также содержится ряд вспомогательньх периферийных устройств. Это два асинхронных UART интерфейса, два I2С интерфейса, синхронный последовательный интерфейс, два интерфейса для чтения смарт карт, интерфейс ИК порта, встроенный таймер общего назначения и три таймера: системный, сторожевой и часов реального времени.

Функциональное описание ИМС uPD61217

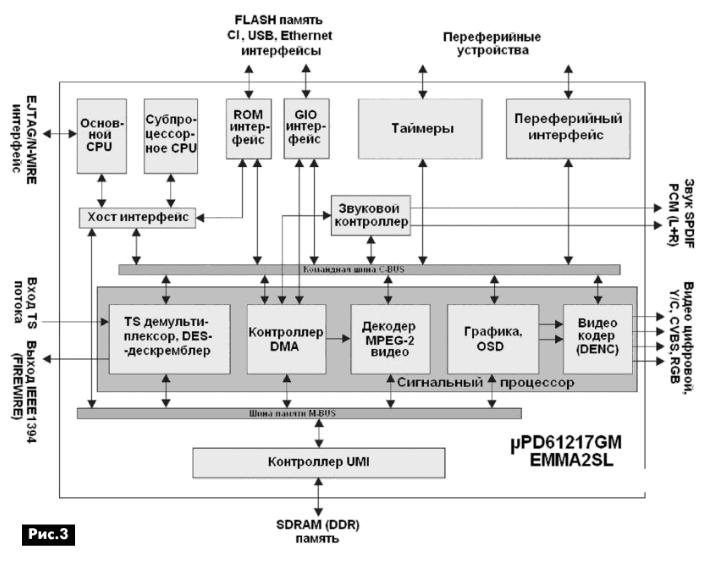

Блок-схема ИМС uPD6121х показана на рис.3 , в её основе лежит двухпроцессорная архитектура с приоритетным разделением выполняемых функций. Основной процессор использует набор RISC команд MIPS II и дополнительные команды MIPS III для проведения следующих операций:

1) умножения деления в блоке MDU (Multiply Divide Unit);

2) для доступа к буферу кэша центрального процессора, используемого для ускорения трансляции адреса виртуальной памяти в адрес физической памяти TLB (Translation Lookaside Butter);

3) для доступа к устройству управления памятью MMU ( Memory Management Unit);

4) проведения операций умножения с накоплением в блоке МАС ( Multipy Accumulate Unit).

Принципиальная электрическая схема основной платы МВ XD-100 REV.08 на основе ИМС uPD6121x приведена на рис.4  Субпроцессор использует набор команд MIPS II и включает в себя 8 Кбайт локальной скратч-памяти и преимущественно используется для декодирования сжатого сигнала звукового сопровождения.

Субпроцессор использует набор команд MIPS II и включает в себя 8 Кбайт локальной скратч-памяти и преимущественно используется для декодирования сжатого сигнала звукового сопровождения.

Поскольку в RISC структурах используется отдельное пространство команд и данных, в ИМС для получения максимального быстродействия процессорных ядер используется двухшинная архитектура с использованием командной шины C-BUS (Command-Bus) и шины памяти M-BUS (Memory Bus). Хост интерфейс осуществляет распределение ресурсов процессорных ядер между памятью, внутренними и внешними устройствами.

ROM интерфейс поддерживает применение как NOR, так и NAND FLASH памяти с общим адресным пространством до 64 Мбайт. Наличие двух выходов выбора кристалла Chip Select (CS) позволяет разбить его на два поля. Каждый из используемых кристаллов FLASH памяти может быть сконфигурирован по объёму 2,4, 8 или 16 Мбайт. В момент выполнения команд, ROM интерфейс освобождает шину памяти, что позволяет увеличить время доступа к внешней SDRAM/DDR памяти узлами сигнального процессора ИМС.

Использование всеми устройствами ИМС единой внешней памяти посредством единого UMI позволило существенно снизить конечную стоимость готовых устройств. Контроллер UMI для µPD61217 помимо поддержки 16-битной SDRAM памяти объемом 8,16,32 и 64 Мбайт, при пропускной способности шины на тактовой частоте 133МГц-250Мбайт/c может обеспечивать функционирование совместно с 16-битной DDRпамятью объемом 16,32,64,128 Мбайт с пропускной способностью шины на тактовой частоте 166МГц до 500Мбайт/c.

Интерфейс GIO обеспечивает доступ к внешним исполнительным устройствам посредством режима прямого доступа. При этом данные между устройствами и основным процессором передаются посредством прямой транзакции через командную шину. Адресное пространство интерфейса равно 8Мбайт и разделено на два поля, выбираемые двумя выходами СS.

Используемая архитектура ROM и GIO интерфейсов позволяет легко подключать к ИМС различные коммуникативные интерфейсы. Это может быть контроллер СI интерфейса (STARCI V2.2 илиCIMAX2.0), USB интерфейса( UBI9022), ENTERNET интерфейса (DM9008AEP) и т.д.

Для отладки конечных устройств, ИМС имеют улучшенный (Tnhanced) JTAG интерфейс – EJTAG. Он позволяет, используя отладочные программы, получить доступ как к регистрам основного процессора, так и субпроцессора, а также ко всей памяти и устройствам, подключаемым к интерфейсам ROM, UMI и GIO для периферийного сканирования (Boundary Scan). Доступ к субпроцессору осуществляется через основной процессор и может быть аппаратно отключен.

Обработка входного сигнала TS в стандартный сигнал видео- и звукового осуществляется блоком сигнального процессора. Он включат в себя: TS-демультиплексор с блоковым фильтром по программным идентификаторам Programm IDientificators (PID), дескремблерсигналов с условным доступом Condition Acctss (CA), стандартный декодер МР@MLMPEG-2, двухмерный графический DitBLitter процессор, поддерживающий режим вставки On Screen Display (OSD), цифровой DENC кодер, обеспечивающий вывод видеосигнала в аналоговой и цифровой форме, а также звуковой контроллер.

Скорость входного TS потока может достигать значения 100Мбит/c. Сигнал возможно вывести на внешние устройства через скоростной интерфейс ІЕЕЕ1394. Выделение требуемой программы происходит следующим образом. Блок фильтров производит PID фильтрацию для одного видео-, двух звуковых, одного PCR (Programm Clock Referens – данные для восстановления синхронизирующего сигнала) или 32-х основных идентифыкаторов PID. Также имеется 32-секционный фильтр размером по 8 байт, организующий 16-байтную фильтрацию. TS демультиплексор восстанавливает данные и тактовую частоту путем использования петли ФАПЧ для контроля частоты внешнего задающего генератора ( с использованием ШИМ выхода).

Если декодируется программа в режиме СА, то сигнал выделенной программы подается на DES дескремблер и систему валидации прав просмотра программы. Результирующий поток передается через UMI интерфейс в циркулярный буфер, организованный во внешней памяти. Данные из циркулярного буфера используются видеодекодером для получения сигнала изображения, субпроцессором для декомпрессии звука и основным процессором для управления системой в целом. Для поддержания процесса арбитрирования доступа к внешней памяти служит контроллер прямого доступа к памяти DMA. Он обеспечивает передачу потоков видеоданных в MPEG-2 декодер, аудиоданных в субпроцессор, передачу данных через GIO интерфейс, а также блоковый обмен между различными участками внешней памяти.

Декодер MPEG-2 декомпрессирует видеоданные по основному профилю и основному уровню (MainProfil@MainLevel) в несжатый цифровой видеосигнал. Данные изображений стандартов MPEG-1 и MPEG-2 с разрешающей способностью 720×480 60Гц и 720×576 50Гц обрабатываются в реальном времени. Для преобразования форматов изображения декодер осуществляет горизонтальную и вертикальную интерполяцию и фильтрацию сигналов.

Звуковой контроллер с помощью ресурсов субпроцессора преобразует скомпрессированный сигнал по слоям Layers 1,2 в несжатый цифровой стереоРСМ и последовательный SPDIF (IEC60958) сигналы. Выходной стереоРСМ сигнал преобразуется внешним сдвоенным ЦАП в традиционный аналоговый стереосигнал звукового сопровождения.

С выхода декодера MPEG-2 нескомпрессированный сигнал поступает на двухмерный графический процессор, преобразующий его из формата RGB32 в формат YCrCb4:2:2. Для привязки к OSD – сигнал подвергается цветовой коррекции. Пользовательские меню отображаются на экране посредством OSD- графики. Отображаемая информация выводится на экран посредством пяти уровней: декодированное MPEG изображение, «остановленное» STEEL-изображение, два независимых уровня OSD- графики и задний монохромный план. Процессор способен осуществить функцию получения «остановленного» изображения путем захвата кадра из приходящего декодированного видеосигнала, а все пять уровней подвергаются 256-уровневому альфа-микшированию.

Скалер реального времени обеспечивает вертикальное и горизонтальное масштабирование видеосигнала с фактором ¼-1/8 для форматов как 4:2:2, так и 4:2:0. Для этого используется горизонтальный и вертикальный фильтры. Уровни OSD поддерживают CLUT(1, 2, 4 и 8 бит на пиксель) и RGB (12+4 альфа, 15+1 альфа, 16 и 32 бит на пиксель) форматы. Изображение OSD- уровней обрабатывается антифликер-фильтром.

Цифровой DENC- кодер с помощью четырех ЦАП обеспечивает формирование аналоговых ТВ сигналов стандартов PAL (M, N), SECAM или NTSC,а также RGB. YPbPr, YCbCr или Y/С с возможностью активизации системы защиты от нелегального копирования Macrovision 7.1. Также возможен вывод информационных данных посредством функйии VBI, представляющей вставку в видеосигнал врезок телетекста WST, CGMS, WPS, Video ID и скрытых титров Closed Caption. Имеется функция регулировки яркости и контрастности выходного видеосигнала.

Для связи с внешними устройствами имеется ряд периферийных интерфейсов: два последовательных асинхронных UART интерфейса, 45 линий порта ввода-выхода I/O, два интерфейса для чтения смарт-карт (стандарта ISO – 7816, EMW или Mondex), два интерфейса шины I2C (работающие в режиме Multi-Master) трехпроводной синхронный последовательный интерфейс и интерфейс ИК приемника (таймер, измеряющий временной интервал между двумя последовательными срезами импульсов, приходящих с ИК детектора/усилителя).

ИМС имеет четыре таймера различного назначения. Таймер захвата/сравнения в режиме захвата измеряет длительность промежутка между последовательными срезами сигнала на входном выводе, а в режиме сравнения удерживает выходной вывод в соответствующем состоянии в течении установленного промежутка времени. В обоих режимах устанавливается разрешающая способность в пределах 0,217…889мкс. Что при наличии 16-разрядного таймер-счетчика дает возможность программировать временные интервалы 14,22мс…58,25с.

Системный таймер работает подобно таймеру захвата/сравнения, но, устанавливая пределы работы программно, по переполнению генерирует вектор прерывания для основного процессора или субпроцессора.

На кристалле интегрированы часы реального времени (RTC), генерирующие время текущего дня. Разрешающая способность таймера RTC – 1мс. RTC генерируют вектор прерывания по переполнению установленной величины, либо если счетчик будет переполнен после 24ч.

Сторожевой (watchdog) таймер контролирует программный и аппаратный останов системы при зависании. Сторожевой таймер генерирует немаскируемое прерывание, дибо активирует вход аппаратного сброса (вывод RSTOUT).

ИМС могут использовать как внешний образцовый генератор, так и внутренний. Когда используется второй режим к выводам XT1, XT2, подключают кварцевый резонатор с частотой 27МГц и временной нестабильностью ± 50ppm.

Аппаратное конфигурацирование ИМС µРD61217

ИМС µРD61217 выпускается в 216-выводном пластмассовом корпусе LGFP (Low profile Quad Flat Pack) (рис.5). Некоторые выводы, в зависимости от типа ИМС, могут иметь дополнительные функции. ИМС имеют пять основных групп выводов:

— напряжения питания и корпусные;

— контрольные выводы, при сбросе задают основные параметры работы ИМС (тактовая частота,

формат обращения к памяти и т.д.), а в рабочем режиме выполняют иные назначенные функции;

— выделенные выводы ( их выполняемые функции постоянны);

— выводы, зарезервированные под интерфейсы, активизирующиеся по умолчанию, но с возможностью переназначения на них дополнительных функций других интерфейсов;

— выводы других интерфейсов.

Наиболее интересным является назначение контрольных выводов RDATA0 – RDATA15 и RADD21 – RADD22, поскольку по их конфигурации можно узнать режимы работы устройств, собранных на описываемых ИМС.

Режимы устанавливаются путем подачи на соответствующие выводы с помощью подтягивающих резисторов логических «0» или «1». В зависимости от установленных на указанных выводах уровней инициализируются следующие режимы.

RDATA0 – установка режима записи байтов многобайтных чисел для основного процессора: 0 – Little Endian (от младшего к старшему), 1 – Big Endian (от старшего к младшему).

RDATA[2: 1] – установка режима объединения содержимого 16-битного буфера ошибок для основного процессора (обычно устанавливается значение 00h).

RDATA3 – зарезервировано для текстового режима (при сбросе должно иметь низкий логический уровень).

RDATA[5: 4] –установка тактовой частоты основного процессора и субпроцессора: 00 — 127.008МГц; 01 — 162МГц; 10 -165.888МГц; 11 – 186МГц.

RDATA[7:6] – установка тактовой частоты SDRAM/DDR.

RDATA8 – установка режима записи байтов многобайтных чисел для ROM интерфейса: 0 – Little Endian , 1 – Big Endian.

RDATA[10:9] – установка объема NAND FLASH памяти и разрядность ROM интерфейса: 00 — <=256Мбит 16 бит, 01 — <=256Мбит 8 бит, 10 — =>512 Мбит 16бит, 11 — =>512 Мбит 8бит.

RDATA10 – ВООТ загрузка: 0 – из внешней NOR FLASH, 1 – из внутренней BOOT ROM.

RDATA[12:11] – ВООТ загрузка из NAND FLASH:00, 01 и 10 – зарезервировано, 11 – загрузка из NAND FLASH.

RDATA13 – режим JTAG:0 – JTAG,1 – EJTAG.

RDATA14 – разрешение последовательного включения контролируемых процессоров для EJTAG (режим «гирлянды»):0 — >основной процессор >субпроцессор, 1 — >основной процессор.

RDATA15 – конфигурация вывода DINTEN для EJTAG:0 – выключен, 1 – включен.

RADD[22:21] – установка образцового генератора: 00 – внутренний генератор; 01 – внешний генератор; 10,11 – зарезервировано.

Принципиальная схема и конструкция ресиверов

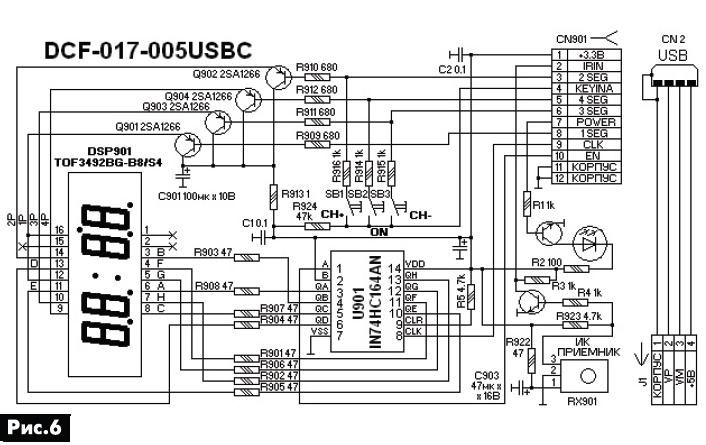

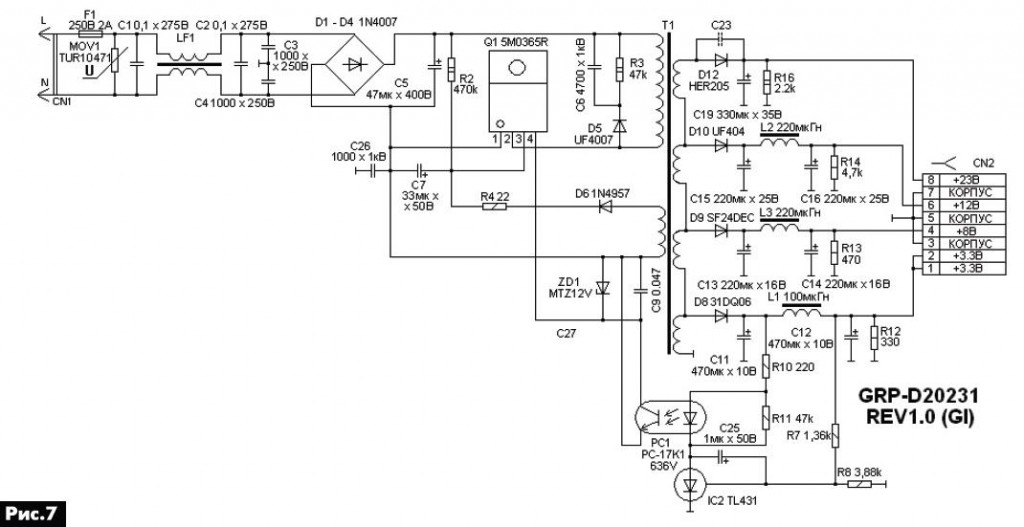

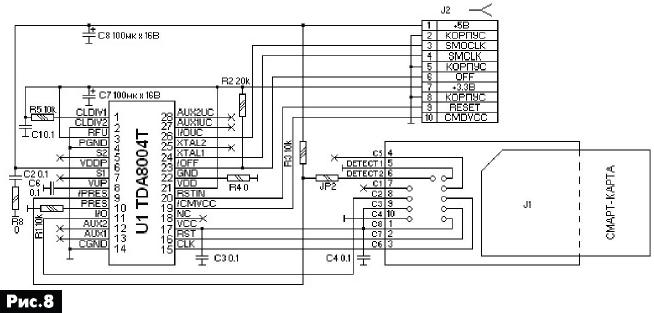

Ресиверы собраны по стандартной схеме компоновки. РесиверGI – S70CR собран на четырех печатных платах: основная плата MB XD – 100REV.08 (рис.4), плата панели управления (рис.6), плата источника питания GRP – D20231 REV1.0 (GI), обеспечивающего преобразование сетевого переменного напряжения в постоянные напряжения для питания узлов ресиверов (рис.7) и плата картридера (рис.8).

Ресивер GI – S805CI собран на трех печатных платах: основная плата MB XD – 300 REV.01A (рис.9), плата панели управления DCF – 017 – 005USBC (рис.6), плата источника питания GRP – D20232 REV1.0 (рис.10). В плате панели управления ресивера GI – S805CI кнопки SB1, SB2 и SB3 имеют обозначение SW903, SW901и SW902.

Ресивер GI – S805CI собран на трех печатных платах: основная плата MB XD – 300 REV.01A (рис.9), плата панели управления DCF – 017 – 005USBC (рис.6), плата источника питания GRP – D20232 REV1.0 (рис.10). В плате панели управления ресивера GI – S805CI кнопки SB1, SB2 и SB3 имеют обозначение SW903, SW901и SW902.

Входной NIM модуль обоих ресиверов TU201 имеет стандартный вход первой ПЧ (950….2150 МГц) и выход LOOP для подключения второго (ведомого) ресивера. При переводе ресивера в режим STANDBY, управление поляризацией наружного конвертора и переключение поддиапазонов производится ведомым ресивером. (При полном обесточивании ресивера контроль наружного конвертора ведомым ресивером невозможен.)

Управление ИМС РЧ преобразователя и QPSK демодулятора осуществляется по шине І2С центральным процессором ИМС U1.

Для формирования напряжения питания внешнего конвертора, управления поляризацией приема используют ИМС линейного стабилизатора U505. Ключ на Q507и Q508 используется для включения/выключения

инжектируемого в кабель снижения напряжения. Если на базу QL508 с U1 подается лог. «1» , то разрешается подача питания на конвертор. Ключ на Q509 осуществляет выбор принимаемой поляризации путем управления напряжением стабилизации U505. инжекция сигнала 22кГц и сигналов протокола DiSEgC осуществляется внутренними элементами модуля TU201. Транзистор Q508 осуществляет контроль замыкания центральной жилы кабеля снижения на оплетку. Самовосстнавливающийся предохранитель RV1 служит для защиты силовых цепей ресивера от короткого замыкания в кабеле снижения.

В ресивере GI – S805CI c выхода TU201 сигнал TS поступает на контроллер CI интерфейсов U20. Контроллер обеспечивает коммутацию CI слотов, подает на соответствующий слот сигнал TS с QPSK демодулятора TU201 и передает дескремблированный сигнал с выбранного слота на вход демультиплексора в составе U1. в ресивере GI – S770CR эти цепи отсутствуют, а сигнал TS подается непосредственно на TU201.

ИМС U1 имеет встроенный ГУН со стабилизацией внешним кварцевым генератором Y2 частотой

27МГц. Из образцовой частоты внутренние схемы U1 формируют частоты для работы процессорного ядра, субпроцессора, внутренних узлов, внешней FLASH и DDR памяти. Сброс ресивера при включении осуществляет цепь U7Q13. Ядра процессора и субпроцессора, входящих в состав ИМС U1, питаются от напряжения 1,5 В, формируемого ИМС линейного стабилизатора U10. периферийные узлы U1 питаются напряжением 3,3В от основного источника питания.

Ресивер управляется ИМС U1, управляющая программа записывается в 16 Мбит FLASH память U201 (M29W160ET ST Microelectronics SPANSION). Управляющую программу можно модифицировать с помощью интерфейса RS-232 без модификации загрузчика (ВООТ секторов). Уровни интерфейса RS-232 сопрягаются с уровнями, необходимыми для работы U1, с помощью ИМС U3 ILX232D фирмы TEXAS INSTRUMENTS. На основной плате установлен разъем EJTAG интерфейса, который позволяет осуществить полное перепрограммирование U201. К 16- битному SDRAM/DDR интерфейсу U1 подключена 256 Мбит ИМС DDR333 ОЗУ U103 ( HYB25DC256160CE – 6 фирмы INFENION или QUIMONDA), используемая MPEG-2 декодером, управляющим процессором и DENC кодером. ИМС энергонезависимого EEPROM U5 24C02WI ( фирмы ATMEL) сохраняет промежуточные пользовательские настройки, а также участвует в процессе авторизации системы условного доступа просмотра платных ТВ каналов.

Автор: Василий Федоров, г. Липецк

Источник: Радиоаматор №6, 2014