Дискриминатор, схема и работа которого рассмотрены в этой статье, предназначен для демодуляции сигналов с широтно-импульсной модуляцией. Он может найти применение в автоматике, в бытовой технике и т.д.

Характеристика дискриминатора линейна относительно «нуля», которому соответствует скважность Q=2 импульсов на его входе.

Напомню, что скважностью называется отношение периода следования импульсов к их длительности: Q=T/t,

где Т – период следования импульсов, t – длительность импульса.

Величина, обратная скважности, называется коэффициентом заполнения. В зарубежной технической литературе этот параметр называется Duty Cycle и сокращенно обозначается как DC. Отсюда DC=1/Q=t/T.

Betrieb

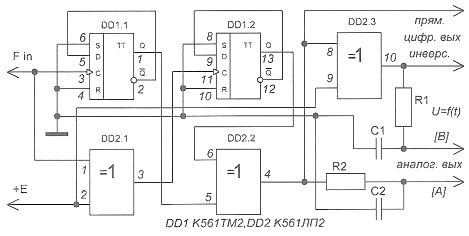

ШИМ дискриминатор может быть собран на двух КМОП-микросхемах DD1 типа К561ТМ2 и DD2 типа К561ЛП2. При изменении длительности входных импульсов (при отклонении их формы от «меандра») на цифровых и аналоговых выходах появляются сигналы, пропорциональные величине отклонения. Устройство содержит противофазные цифровые и аналоговые выходы. В зависимости от применения устройства лишние выходы можно исключить.

Принципиальная электрическая схема устройства показана на Figur 1.

Оно состоит из:

- двух делителей частоты на 2 (счетных триггеров), выполненных на D-триггерах DD1, DD1.2;

- фазового детектора на элементе DD2;

- двух инверторов 1, DD2.3.

Входной ШИМ сигнал поступает на тактовый вход С триггера DD1.1 непосредственно, а на тактовый вход С второго триггера DD1.2 через инвертор DD2.1. Как известно, подача высокого уровня напряжения на один из входов логического элемента «Исключающее ИЛИ» превращает его в инвертор. D-триггеры срабатывают по положительному фронту входных импульсов.

В результате деления двух противофазных сигналов на прямых выходах D-триггеров появляются две сдвинутые импульсные последовательности вида «меандр». Работа фазового детектора DD2.2 основана на таблице истинности логического элемента «Исключающее ИЛИ». Выходной сигнал этого элемента равен лог «1» в случае отличия входных сигналов друг от друга и равен лог. «0» в случае совпадения входных сигналов. Сдвиг фаз этих последовательностей пропорционален длительности входного импульса и находится в пределах 0«φ<180°.

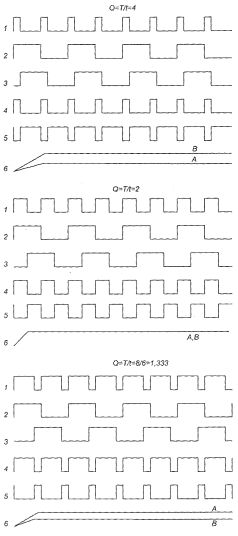

Von Figur 2 показаны временные диаграммы сигналов в шести точках устройства для различных значений скважности входного сигнала.

На этом рисунке цифрами обозначено:

- – входной сигнал;

- – сигнал на прямом выходе первого триггера (вывод 1 DD1.1);

- – сигнал на прямом выходе второго триггера (вывод 13 DD2);

- – сигнал на прямом выходе фазового детектора (вывод 4 DD2);

- – сигнал на инверсном выходе фазового детектора (вывод 10 DD3);

- – выходные аналоговые сигналы: точка А – прямой, точка В – инверсный.

Аналоговые выходные сигналы получаются после интегрирования прямого и инверсного сигналов фазового детектора интегрирующими цепочками R2С2 и R1С1 соответственно. Постоянную времени этих цепочек выбирают исходя из области применения дискриминатора.

При напряжении питания 12 В входная частота может достигать 10 МГц.

В заключение замечу, что рассмотренная схема может быть и для демодуляции ЧМ сигналов, если этот ЧМ сигнал будет предварительно преобразован в ШИМ сигнал, но это тема отдельной статьи.

Fachliteratur

- Широтно-импульсный дискриминатор // Радио. – 1994. – №4. – С.43.

Autor: Wjatscheslaw Kalashnik, Voronezh